集成電路的發(fā)展趨勢(shì)已由追求性能和集成度提升為主轉(zhuǎn)變成以降低功耗為主,而降低功耗的最有效方法即降低工作電壓。目前,互補(bǔ)金屬氧化物半導(dǎo)體(complementary metal-oxide semiconductor, CMOS)集成電路(14/10 nm技術(shù)節(jié)點(diǎn))的工作電壓降低至0.7 V,而MOS晶體管中亞閾值擺幅(subthreshold swing, SS)的熱激發(fā)限制(60 mV/DEC)導(dǎo)致集成電路的工作電壓無(wú)法縮減到0.64 V以下。現(xiàn)有能實(shí)現(xiàn)SS<60 mv/dec的晶體管主要有隧穿場(chǎng)效應(yīng)晶體管(tunneling field-effect transistor, tunneling fet)和負(fù)電容場(chǎng)效應(yīng)晶體管(negative capacitance fet)兩類(lèi),它們有著速度低或穩(wěn)定性差、不宜集成等重要缺陷,缺乏實(shí)用價(jià)值。而用于未來(lái)集成電路的超低功耗晶體管不僅需要實(shí)現(xiàn)ss<60 mv/dec,保證開(kāi)態(tài)電流足夠大,還要求性能穩(wěn)定,制備簡(jiǎn)單。

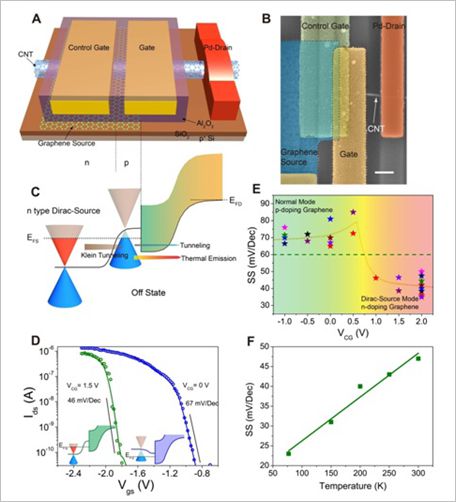

北京大學(xué)電子學(xué)系、納米器件物理與化學(xué)教育部重點(diǎn)實(shí)驗(yàn)室張志勇教授、彭練矛教授課題組重新審視了MOS晶體管亞閾值擺幅的物理極限,提出一種新型超低功耗的場(chǎng)效應(yīng)晶體管,并采用具有特定摻雜的石墨烯作為一個(gè)“冷”電子源,用半導(dǎo)體碳納米管作為有源溝道,以高效率的頂柵結(jié)構(gòu)構(gòu)建出狄拉克源場(chǎng)效應(yīng)晶體管(Dirac source-FET, DS-FET),在實(shí)驗(yàn)上實(shí)現(xiàn)室溫下40 mV/DEC左右的亞閾值擺幅。變溫測(cè)量結(jié)果顯示,DS-FET的亞閾值擺幅與溫度呈明顯線(xiàn)性關(guān)系;這表明晶體管的載流子輸運(yùn)是傳統(tǒng)熱發(fā)射,而不是隧穿機(jī)制。DS-FET具有優(yōu)秀的可縮減性,當(dāng)器件溝道長(zhǎng)度縮至15 nm時(shí),仍可穩(wěn)定地實(shí)現(xiàn)亞60 mV/DEC的亞閾值擺幅。

最為重要的是,DS-FET具有與金屬-氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(metal-oxide-semiconductor field-effect transistor, MOSFET)相比擬的驅(qū)動(dòng)電流,遠(yuǎn)高于隧穿晶體管,且其SS<60 mv/dec所跨的電流范圍更大。作為亞60 mv/dec開(kāi)態(tài)和關(guān)態(tài)特性綜合指標(biāo)的關(guān)鍵參數(shù)(即ss="60" mv/dec時(shí)的電流),i60="40" μa/μm,是已發(fā)表的最佳隧穿晶體管的2000倍,完全達(dá)到了國(guó)際半導(dǎo)體發(fā)展路線(xiàn)圖(itrs)對(duì)亞60 mv/dec器件實(shí)用化的標(biāo)準(zhǔn)。典型狄拉克源晶體管在0.5 v工作電壓下的開(kāi)態(tài)和關(guān)態(tài)電流均與英特爾公司14 nm技術(shù)節(jié)點(diǎn)cmos器件(在0.7 v工作電壓下)相當(dāng);這表明狄拉克源晶體管能夠滿(mǎn)足未來(lái)超低功耗(vdd<0.5 v)集成電路的需要。而且,這種狄拉克源的器件結(jié)構(gòu)不依賴(lài)半導(dǎo)體材料,有望用于傳統(tǒng)cmos晶體管和二維材料的場(chǎng)效應(yīng)晶體管,具有普適性。

采用雙柵控制實(shí)現(xiàn)的狄拉克源晶體管結(jié)構(gòu)和性能表征,其中半導(dǎo)體碳納米管作為器件的有源溝道,源端采用一個(gè)控制柵來(lái)調(diào)節(jié)石墨烯的費(fèi)米能級(jí)

2018年6月14日,上述工作以《作為高能效和高性能電子開(kāi)關(guān)的狄拉克源場(chǎng)效應(yīng)晶體管》(Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches)為題,在線(xiàn)發(fā)表(first release)于《科學(xué)》(Science,DOI: 10.1126/science.aap9195)。第一作者為北京大學(xué)信息科學(xué)技術(shù)學(xué)院“博雅”博士后項(xiàng)目入選者邱晨光博士,張志勇教授和彭練矛教授為共同通訊作者;香港大學(xué)物理系劉飛博士和麥吉爾大學(xué)物理系郭鴻教授提供了理論仿真支持,北京大學(xué)化學(xué)與分子工程學(xué)院彭海琳教授課題組提供了部分石墨烯材料。狄拉克源晶體管的發(fā)明突破了晶體管室溫亞閾值擺幅的熱發(fā)射理論極限,提供了一種能夠?qū)崿F(xiàn)室溫下亞60 mV/DEC的新原理結(jié)構(gòu);與此同時(shí),還能保持傳統(tǒng)MOS晶體管的高性能,有望將集成電路的工作電壓降低到0.5 V及以下,為3 nm以后技術(shù)節(jié)點(diǎn)的集成電路技術(shù)提供解決方案。

相關(guān)研究得到國(guó)家自然科學(xué)基金創(chuàng)新研究群體、國(guó)家重點(diǎn)研發(fā)計(jì)劃“納米科技”重點(diǎn)專(zhuān)項(xiàng),以及北京市科學(xué)技術(shù)委員會(huì)等資助和支持。